گروهی متشکل از محققان دانشگاه کالیفرنیا و دانشگاه ایلینویز دریافتهاند که میتوان برد مدار چاپی را با بستری از جنس سیلیکون یعنی همان مادهای که تراشهها از آن ساخته میشوند جایگزین کرد. چنین راهکاری امکان ساخت سامانههای پردازشی سبکتر و کوچکتر و سامانههایی با توان پردازشی بسیار بالاتر را فراهم خواهد کرد. در این راهکار که Si-IF سرنام (silicon-interconnect fabric) نام دارد، تراشههای سیلیکونی و سایر اجزای مورد نیاز برای کار سختافزار بهطور مستقیم بر بستری از جنس سیلیکون نصب میشوند. در این روش بر خلاف برد مدار چاپی، سیمبندی بین اجزای مدار به همان ظرافت سیمبندی درون تراشه است. نتیجه بدیهی چنین ظرافتی در سیمبندی، این است که میتوان اتصالات بیشتری بین تراشهها برقرار کرده و با صرف توان کمتر، دادهها را با سرعتی بیشتر منتقل کرد.

Si-IF مزیت دیگری هم دارد. فرآیند دشوار و پیچیده پیادهسازی سیستم روی تراشه (SoC) را سادهتر میکند. SoC در ابزارهای امروزی از گوشیهای هوشمند گرفته تا ابرکامپیوترها استفاده میشود. حالا طراحان میتوانند مجموعهای از چیپلتهای (یا به بیان این محققان دایلت) کوچکتر که طراحی و تولید آنها سادهتر است را روی بستر سیلیکونی با یکدیگر مرتبط کنند. امروزه شرکتهایی نظیر اِیاِمدی، اینتل و انویدیا روی توسعه چیپلتها کار میکنند و ایده Si-IF مسیر فوق را هموارتر خواهد کرد.

کابوس بستهبندی تراشه

برای درک بهتر اهمیت حذف برد مدار چاپی از طراحی سامانههای پردازشی نگاهی به یک SoC مرسوم میاندازیم. در حال حاضر میتوانیم بخش زیادی از آنچه برای بهکار انداختن یک گوشی هوشمند نیاز داریم را روی تکهای از سیلیکون به مساحت یک سانتیمتر مربع جای دهیم. با فناوریهای فعلی، برای اینکه بتوانیم تراشه را به سایر قطعات سختافزار متصل کنیم و ارتباط بین تراشه و این اجزا را برقرار کنیم، مجبوریم تراشه را در بستهای که معمولا پلاستیکی است و ممکن است ۲۰ برابر بزرگتر از خود تراشه باشد قرار دهیم و خروجیهای بسیار ظریف تراشه را از طریق پایههایی به بیرون این بسته برسانیم. این تفاوت قابلتوجه در اندازه تراشه و محفظهاش دستکم دو مشکل دارد. نخست اینکه تراشه بستهبندی شده، فضای بسیار بیشتری روی مدار اشغال میکند و وزن بیشتری نسبت به خود تراشه خواهد داشت و این مسئله در طراحیهایی که ظرافت و وزن دستگاه حائز اهمیت است، چالش بزرگی محسوب میشود. مشکل دوم این است که اگر سختافزار مورد نظر به چند تراشه نیاز داشته باشد مسافتی که سیگنالها باید در مدار طی کنند چند برابر افزایش مییابد. بنابراین ما در روش مرسوم طراحی و پیادهسازی، از یک سو سرعت پردازش را بهطور چشمگیری کاهش دادهایم و از سوی دیگر میزان مصرف انرژی را بالا بردهایم. این گلوگاههای سختافزاری در کاربردهایی نظیر کارهای گرافیکی، یادگیری ماشین و جستوجو که با حجم زیادی از داده سروکار داریم بسیار به چشم میآیند و چالشهای بزرگی هستند. خنکسازی تراشههای بستهبندی شده دشوار است، زیرا سالهای متمادی است که این عامل بهعنوان یک عامل محدودکننده در طراحی سامانههای کامپیوتری شناخته میشود. حالا پرسش این است که اگر بستهبندی تراشهها چنین مشکلاتی بوجود میآورد پس چرا تراشه را بستهبندی میکنیم؟ دلیل آن، وجود برد مدار چاپی است.

راهی به سوی طراحی بدون برد مدار چاپی

هدف از بهکارگیری برد مدار چاپی فراهم کردن بستری برای برقراری اتصال بین تراشهها و دیگر قطعات الکترونیکی است، اما در کاربردهای امروزی این روش بهترین گزینه نیست. ساخت بردهای مدار چاپی کاملا مسطح، دشوار است و ممکن است در روند تولید، سطح آنها تاب بردارد. تراشههای بستهبندی شده معمولا توسط لحیمکاری به برد متصل میشوند. به دلیل محدودیتهای لحیمکاری و مشکل تاب برداشتن سطح (warpage) نمیتوانیم فاصله بین نقاط لحیمکاری را به کمتر از نیم میلیمتر برسانیم. به بیان دیگر در هر سانتیمتر مربع از مساحت تراشه، نمیتوان بیش از ۴۰۰ اتصال را گنجاند. در بسیاری از کاربردها این تعداد اتصالات برای رساندن برق به تراشه و ورود و خروج سیگنالها کافی نیست. طراحان با بستهبندی تراشه و در حقیقت با افزایش فضا، سعی میکنند امکان برقراری اتصالات بیشتری را به ازای واحد سطح فراهم کنند. بدین ترتیب خواهیم توانست اتصالات ظریف روی تراشه که حدود ۱ تا ۵۰ میکرومتر هستند را به اتصالات ۵۰۰ میکرومتری روی PCB متصل کنیم.

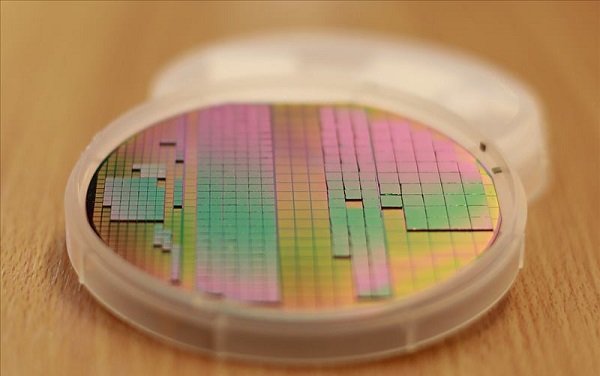

به عقیده محققان، بهترین راهکار این است که تراشهها بدون بستهبندی و نصب کردن روی PCB، بهطور مستقیم روی یک ویفر سیلیکونی نازک به ضخامت ۵۰۰ میکرومتر تا ۱ میلیمتر نصب شوند. پردازندهها، قطعات حافظه، چیپلتهای آنالوگ و RF، ماژولهای تنظیم ولتاژ و حتی قطعاتی نظیر سلفها و خازنها را میتوان بهطور مستقیم روی این بستر سیلیکونی نصب کرد. در مقایسه با مواد بهکار رفته در ساخت بردهای مدارچاپی معمول، یک ویفر سیلیکونی مقاومتر است و میتوان آنرا مسطحتر از PCB ساخت و مشکل تاب برداشتن برد را حل کرد. علاوه بر این بهدلیل اینکه تراشه و بستری که تراشه روی آن نصب شده از یک جنس (سیلکون) هستند تأثیر تغییرات دما روی این دو یکسان است و با یک نسبت منبسط و منقبض میشوند در نتیجه به اتصالات بزرگ و انعطافپذیر نظیر نقاط لحیمکاری بین تراشه و بستر نیازی نیست. در چنین شرایطی میتوان بهجای نقاط لحیمکاری از پین مسی (pillar) استفاده کرد که داخل بستر سیلیکونی کار گذاشته میشوند و ابعادی در حد میکرومتر دارند. با اعمال همزمان نیرو و حرارت، پورتهای مسی ورودی و خروجی تراشه بهطور مستقیم توسط این پینهای مسی، روی بستر سیلیکونی مهار میشوند. اگر اینکار بهطور دقیق انجام شود، اتصالات مطمئنتر و بهصرفهتری نسبت به روش لحیمکاری بهدست میآید.

حذف PCB از طراحی این امکان را میدهد که پورتهای ورودی-خروجی تراشه را در فواصل ۱۰ میکرومتری کنار هم بچینیم که در مقایسه با فواصل ۵۰۰ میکرومتری روش PCB بسیار قابل توجه است. در نتیجه میتوانیم بدون نیاز به بستهبندی، شمار پورتهای ورودی-خروجی تراشه را ۲۵۰۰ برابر کنیم. علاوه بر این، استفاده از روشهای استاندارد تولید نیمههادی امکان پیادهسازی سیمبندیهای چند لایه بسیار ظریف با فواصلی کمتر از ۲ میکرومتر را روی Si-IF فراهم میکنند. در این صورت فاصله فیزیکی بین تراشهها هم به کمتر از ۱۰۰ میکرومتر خواهد رسید که در مقایسه با فواصل ۱ میلیمتری تراشههای نصب شده روی PCB پیشرفت چشمگیری است. نتیجه این خواهد بود که سامانه مبتنی بر Si-IF فضای کمتری اشغال میکند، توان کمتری مصرف میکند و سیگنالها سریعتر به مقصد میرسند. از سوی دیگر برخلاف PCB و مواد مورد استفاده در بستهبندی تراشهها، سیلیکون یک هادی بسیار خوب حرارت است. برای دفع حرارت بیشتر میتوان گرمابرها را در دو طرف Si-IF نصب کرد. دفع بیشتر حرارت این امکان را به پردازندهها میدهد که سریعتر کار کنند.

در مقایسه با PCB، مواد مورد استفاده در روش Si-IF گرانتر هستند. قیمت هر میلیمتر مربع از یک PCB هشت لایه حدود یک دهم قیمت ویفر Si-IF چهار لایه خواهد بود. محققان معتقد هستند که مواردی نظیر حذف هزینه بستهبندی تراشه و هزینه ساخت پیچیده برد مدار و جمعتر شدن طراحی، برتری Si-IF در مقابل PCB را به اثبات میرساند.

شکل۱ - مقایسهای بین Si-IF (سمت چپ تصویر) و روش مرسوم نصب تراشه بستهبندی شده روی برد مدار چاپی (سمت راست). در روش Si-IF، تراشهها با اتصالات بیشتر و متراکمتری به اجزای مدار متصل شده و دفع حرارتی هم بهتر انجام میشود.

به دلیل اتصالپذیری بیشتر و توانایی بالاتر دفع حرارت، در پیادهسازی مبتنی بر Si-IF عملکرد پردازندههای مرسوم دو برابر میشود. سطح مدار سیلیکونی هم از هزار سانتیمتر مربع به چهارصد سانتیمتر مربع تقلیل مییابد. مزایایی که در حوزه دیتاسنترها بسیار اهمیت دارند، زیرا فضای اشغالی و نیاز به زیرساختهای خنکسازی را کاهش خواهند داد. در بررسی سامانههای بسیار کوچکتر از این، یک سامانه اینترنت اشیاء مبتنی بر میکروکنترلر آرم مورد مطالعه قرار گرفت. با استفاده از Si-IF نه تنها اندازه برد ۷۰ درصد کاهش یافت، بلکه وزن آن هم از ۲۰ گرم به ۸ گرم رسید. امکان کوچکسازی طراحیهای فعلی و دستیابی به طرحهای بهینهتر با استفاده از Si-IF وجود دارد. این محققان معتقدند که با Si-IF طراحان میتوانند روی توسعه کامپیوترهایی کار کنند که طراحی و ساخت آنها تاکنون غیرممکن یا غیرمنطقی به نظر میرسیده است.

کمک Si-IF به ساخت پردازندههای غولآسا

بهطور معمول در یک سرور با کارآیی بالا، روی هر PCB دو تا چهار پردازنده وجود دارد، اما در برخی از کاربردهای رایانشی سنگین به چند سرور نیاز است. یک راهکار این است که همه پردازندهها را روی یک ویفر سیلیکونی پیاده کنیم و به چیزی شبیه یک پردازنده بسیار بزرگ و یکپارچه برسیم، اما هرچه ابعاد تراشهای که میسازیم بزرگتر شود احتمال وجود نقص در آن هم بیشتر میشود بهطوریکه رابطهای نمایی بین احتمال وجود نقص در تراشه تولید شده و مساحت آن تراشه برقرار است. در روش Si-IF میتوان چیپلتها که امکان ساخت بدون خطای آنها فراهم است را کنار هم قرار داد و به سامانه پردازشی بزرگتری دست یافت. این گروه از محققان با راهکار Si-IF چنین تراشهای در مقیاس ویفر طراحی کردهاند که ۴۰ پردازنده گرافیکی یا GPU در آن قرار گرفته است. شبیهسازیها نشان دادهاند که این طراحی در مقایسه با یک سیستم مجهز به ۴۰ پردازنده گرافیکی پیشرفته، سرعت محاسبات را بیش از پنج برابر افزایش داده و میزان مصرف انرژی را تا ۸۰ درصد کاهش میدهد. این نتایج قابل قبول به سادگی بهدست نیامدهاند و لازم بود که چند چالش برطرف شود. مواردی نظیر دفع حرارت از روی ویفر، اینکه پردازندههای گرافیکی چگونه میتوانند به بیشترین سرعت ارتباطی با هم دست یابند و چگونگی رساندن برق به بخشهای مختلف ویفر از جمله این چالشها بودهاند (شکل 2).

شکل2 - دایلتها (یا چیپلتها ) بر بستر سیلیکونی Si-IF به هم متصل میشوند. بر خلاف روشهای مرسوم نصب تراشه روی برد مدار چاپی، در این روش جدید دایلتها را میتوان با فاصله صد میکرومتر از هم چید و این، سرعت انتقال سیگنالها را افزایش داده و مصرف توان را کاهش میدهد.

مصرف توان یکی از چالشهای اصلی بود. در صورت تغذیه تراشه با یک ولت، سیمبندی ظریف ویفر مصرف توان را به ۲ کیلووات میرساند. بنابراین از تغذیه ۱۲ ولت استفاده شد تا جریان و در نتیجه مصرف توان کاهش یابد. پیاده کردن این راهکار نیازمند استفاده از تنظیمکنندههای ولتاژ و خازنهای ویژهای بود که باید در جایجای ویفر نصب میشدند. نمونه اولیهای از این سامانه پردازشی به وسعت ویفر ساخته شده و اننتظار میرود نتیجه نهایی تا پایان سال آینده میلادی آماده شود.

SoIF جایگزینی برای SoC

به باور این محققان، Si-IF راهکاری مناسب برای رفع ایراداتی است که طراحان SoC با آنها مواجهاند. دو دهه است که طراحان برای دستیابی به کارایی بهتر و در عین حال کاهش هزینهها تراشههای مستقل در قالب سیستم روی تراشه (SoC) را پیادهسازی میکنند. در این نوع پیادهسازی همانگونه که از نامش پیدا است سعی میشود یک سیستم روی تراشهای گنجانده شود. این راهکار اگرچه مزایایی دارد، اما معایبش قابل توجه است. SoC یک تراشه نسبتاً بزرگ است و هرچه تراشه بزرگتر شود احتمال وجود خطا و نقص در آن بیشتر میشود، بهویژه زمانیکه از فرآیندهای بسیار پیشرفته تولید نیمههادی استفاده میکنیم. هزینه بالای طراحی و تولید اینگونه از تراشهها و اینکه ایجاد یک تغییر جزیی در طراحی یا بهروزرسانی فرآیند تولید آنها نیازمند بازطراحی کل تراشه است از جمله چالشهای سیستمهای روی تراشه است. در استفاده از SoC مجبوریم همه زیرسیستمها را بر اساس یک فرآیند واحد تولید کنیم حتی اگر این امکان باشد تا یکی از زیرسیستمها با فناوری و روش تولید بهتر و بهینهتری تولید شود. در نتیجه برخی یا همه زیرسیستمهای داخلی SoC به نهایت کارآیی و بهرهوری خود نمیرسند.

روش Si-IF این امکان را به طراحان میدهد که اجزای مورد نیاز یک SoC را به دایلتهایی خرد کنند و هر دایلت با فرآیندی که مناسب همان دایلت است طراحی و تولید شود. در این صورت زیرسیستمهای SoC را میتوان در قالب یک سیستم روی ویفر (system-on-wafer) یا سیستم روی Si-IF ( یا system–on–Si-IF) پیاده کرد و از مزایای ساده شدن روند طراحی و کاهش هزینههای تولید بهرهمند شد. میتوان اجزای مورد نیاز را ( که این محققان ترجیح میدهند بجای چیپلت، آنها را دایلت بنامند) بهطور مجزا تولید کرد و بر بستر Si-IF سوار نمود. فاصله این اجزا در مقایسه با فاصله بلوکهای عملیاتی یک SoC مرسوم بسیار کمتر است و چگالی اتصالات هم بالاتر میرود که این برتری ناشی از اندازه بسیار کوچک دایلتها است. تولید دایلتهای کوچک در مقایسه با یک SoC بزرگ ارزانتر تمام میشود، زیرا هرچه سطح تراشه کوچکتر باشد، نقایص کمتر میشوند. در این روش تنها چیزی که ابعاد بزرگی دارد بستر سیلیکونی SoIF است که آن هم مشکلی ایجاد نمیکند. SoIF هر آنچه صنعت با حرکت به سوی چیپلتها خواهان دستیابی به آن است را در اختیار قرار میدهد. بهعنوان مثال ساخت یک SoIF با یک فناوری تولید جدیدتر، ارزانتر و سادهتر انجام میشود. هر دایلت را میتوان با فناوری مناسب خودش تولید کرد و فقط همانهایی که نیاز به بهروزرسانی یا بازطراحی دارند تغییر داده خواهند شد؛ موردی که در روش فعلی طراحی و تولید SoC دور از دسترس است. این نوع مجتمعسازی به طراح این امکان را میدهد تا دایلتهایی از نسلها و فناوریهای مختلف را با هم ترکیب کند و سامانههای کاملاً جدیدی بسازد.

این محققان مدعی هستند که هزینه کلی طراحی و تولید یک SoIF تا ۷۰ درصد کمتر از SoC خواهد بود و این در مواردی است که به تعداد انبوهی از تراشهها نیاز نیست و فقط چند هزار واحد نیاز است (شکل 3).

شکل۳ - مجتمعسازی در مقیاس ویفر با استفاده از Si-IF، پهنای باند را افزایش میدهد و تأخیر را کاهش و در مقایسه با یک سامانه مبتنی بر برد مدار چاپی، مصرف توان کمتری دارد.

همین کاهش هزینههای طراحی و کوچکسازی سبب میشود که طراحی سیستمهای سفارشی شده با کمک SoIF سادهتر باشد. این محققان بر این باور هستند که کاهش هزینه و در دسترس بودن چنین امکانی سبب خواهد شد که شاهد نوآوریهای بیشتری باشیم و این برای طراحان، استارتآپها و دانشگاهها مفید خواهد بود.

مسیری رو به آینده

در چند سال گذشته این محققان برای بهبود روند مجتمعسازی Si-IF تلاش زیادی کردهاند، اما هنوز در ابتدای مسیر هستیم. یافتن راهی مقرون به صرفه برای تولید بر اساس این فناوری نخستین موردی است که باید حل شود. ارائه راهکاریی مناسب برای آزمودن دایلتهای تولید شده و بردهای Si-IF هم مورد دیگری است که باید به آن پرداخت. یافتن روشهای جدیدتر دفع حرارت با توجه به رفتار سیلیکون در مقابل افزایش دما موضوع مهم بعدی است. این محققان بدین منظور راهکاری یکپارچه برای خنکسازی و برقرسانی در مقیاس ویفر (PowerTherm) عرضه کردهاند. بدنه و زیرساختهای نصب، کانکتورها و کابلکشی برای ساخت کل سیستم نیازمند طراحی ویژهای است و پیادهسازی و اجرای تراشه هم روشهای طراحی و معماری خاص خود را میطلبد. موضوع مهم این است که باید به قابلیت اطمینان این طراحی هم دقت کرد و راهی برای دستیابی به بالاترین میزان اطمینان یافت. اگر یکی از دایلتها پیش از پیادهسازی روی سامانه دچار اشکال شوند یا ناقص باشند یا در حین کار دچار مشکل شوند تعویض آن بسیار دشوار خواهد بود. نکته مهمی که در پیادهسازی SoIF باید به آن توجه داشت انتخاب صحیح دایلتهایی است که میتوان در کنار هم قرار داد. شما نمیتوانید برای همه زیرسیستمهای یک SoC از دایلت مشابهی استفاده کنید. به بیان دیگر باید با بررسی طراحیهای موجود و مرسوم، قابلیتها و عملکردهایی را شناسایی کنیم که تمایل بیشتری دارند بهطور فیزیکی در نزدیکی هم پیادهسازی شوند. در صورتی که این عملکردها با فرآیند مشابهی قابل تولید باشند و بهروزسانی آنها بهطور مشابهی قابل اجرا باشد، میتوان آنها را در یک دایلت گنجاند و مجتمعسازی کرد.

اگر چه این موارد و موارد دیگر، فهرستی بلند بالا از چالشها را پدید میآورند، اما محققان بهطور جدی مشغول رفع این چالشها هستند و شاید در آیندهای نه چندان دور، شاهد یک تغییر اساسی در سختافزار کامپیوترها و ابزارهای همراهمان باشیم.

ماهنامه شبکه را از کجا تهیه کنیم؟

ماهنامه شبکه را میتوانید از کتابخانههای عمومی سراسر کشور و نیز از دکههای روزنامهفروشی تهیه نمائید.

ثبت اشتراک نسخه کاغذی ماهنامه شبکه

ثبت اشتراک نسخه آنلاین

کتاب الکترونیک +Network راهنمای شبکهها

- برای دانلود تنها کتاب کامل ترجمه فارسی +Network اینجا کلیک کنید.

کتاب الکترونیک دوره مقدماتی آموزش پایتون

- اگر قصد یادگیری برنامهنویسی را دارید ولی هیچ پیشزمینهای ندارید اینجا کلیک کنید.

نظر شما چیست؟