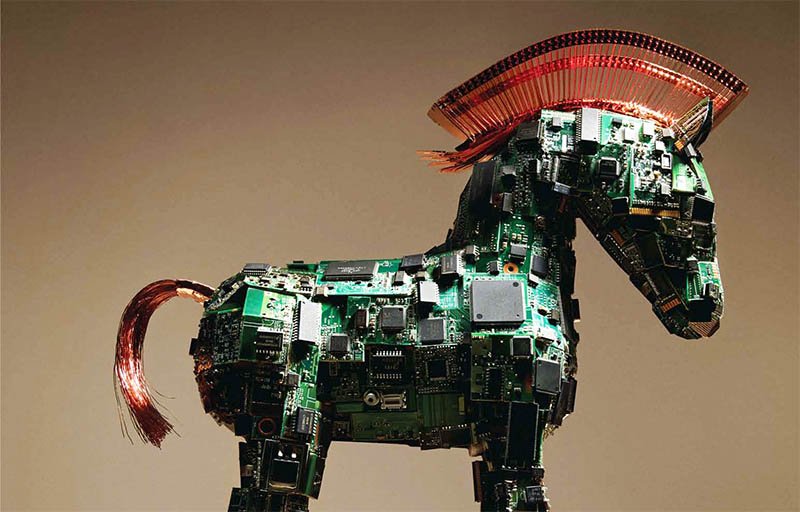

برای درک ماهیت یک تروجان سختافزاری میتوان دقیقاً بهنام آن توجه کرد؛ تغییر کوچکی در یک مدار یکپارچه که ممکن است به ایجاد اختلال در عملکرد تراشه منجر شود. با یک طراحی مناسب، یک نفوذگر باهوش میتواند تراشه را به گونهای تغییر دهد تا در لحظه حساس عملکرد خود را از دست بدهد یا سیگنالهای اشتباه ایجاد کند. همچنین، فرد مهاجم قادر خواهد بود تا با ایجاد یک در پشتی کلیدهای رمزگذاری یا رمزهای عبور را شنود یا اطلاعات داخلی تراشه را به خارج از مجموعه ارسال کند. دلایل محکم زیادی برای نگرانی در این زمینه وجود دارد. در سال 2007، یک سامانه رادار مرزی در آسیا در صدور پیام اخطار در برابر حمله هوایی دچار خطا شد. شایعههایی وجود دارد که میگوید ایجاد یک در پشتی روی یکی از تراشههای سیستم باعث به وجود آمدن آن خطا شده بود.

مطلب پیشنهادی: کوالکام تراشه یادگیرنده امنیتی ساخت

ادعاهای جدی دیگری نیز درباره حمله از طریق اضافه کردن مدارها مطرح شده است. افزایش روزافزون گزارشهای مربوط به وجود تراشههای جعلی، پرسشهایی را درباره میزان قابل اعتماد بودن زنجیره تأمین مدارهای مجتمع در جهان مطرح کرده است. چنانچه هر کدام از این حدس و گمانها به بروز یک فاجعه منجر شوند، نقش تروجانها در تاریکی باقی خواهد ماند. در واقع، اگر یکی از این تروجانهای «بالقوه تهدیدآمیز» سختافزاری در جایی پیدا شده باشد، هنوز اخبار آن بهطور عمومی به بیرون درز پیدا نکرده است. مشخصاً اگر این تراشه در مکان مناسب قرار بگیرد، این قابلیت را دارد تا یک سیستم دفاعی را دور بزند، اطلاعات خصوصی ما را در سراسر جهان منتشر کند و یک نیروگاه یا بخشی از یک شبکه بزرگ برق را از کار بیاندازد.

منابع تحقیقاتی زیادی صرف درک بهتر ابعاد این مشکل شدهاند، اما راهحلها یکی یکی در حال پدیدار شدن هستند. در سال 2011، «برنامه پروژههای تحقیقاتی پیشرفته هوشمند» (IARPA سرنام Intelligence Advanced Research Projects Activity) در ایالات متحده، برنامه جدیدی را برای یافتن روشهای تشخیص تراشههای مطمئن آغاز کرد. گروه ما از دانشگاه استنفورد بهعنوان بخشی از این پروژه همکاری خود را با دیگر گروههای تحقیقاتی آغاز کرد. موضوع فعالیت ما ایجاد تغییرات ساختاری در روش طراحی و تولید مدارهای مجتمع است.

هماکنون تمرکز ما روی ایجاد محافظت در مقابل تروجانهای سختافزاری از طریق بررسی دقیق مکانهای تولید تراشه و محدود کردن فرصت هر گونه شرارت و اخلالگری از طریق محدود ساختن سازندگان تراشهها در یک دایره متشکل از افراد و شرکتهای معتبر و مطمئن صورت میگیرد. اگر این تحقیقات به موفقیت منتهی شود، این امکان فراهم خواهد شد تا بتوان طراحی و ساخت تراشه را با خاطری آسوده و اطمینان از تبانی نکردن و لو رفتن امنیت کسبوکار، به فردی بسپاریم که مایل باشیم. علاوه بر این، تحقیقات ما به یافتن راههایی برای استفاده از تراشهها، حتی با وجود یک تروجان سختافزاری در داخل آن منتهی خواهد شد.

تراشههای امروزی پیچیدگیهای زیادی دارند و هزینه بالای طراحی و ساخت آنها باعث میشود تا یک شرکت به تنهایی و بدون استفاده از کمک دیگران قادر نباشد آنها را بسازد. شاید یک شرکت کوچک بتواند توزیع و بازاریابی مدارهای مجتمع را برعهده بگیرد، اما معمولاً توزیع راهبردی برای معرفی یک طراحی جدید بر عهده دیگر شرکتها خواهد بود. هنوز هم شاید دیگر شرکتها دستی در تولید، بستهبندی و توزیع تراشهها داشته باشند.

در این میان و با افزایش تعداد متعاملان، فرصت دستاندازی و مداخله در سختافزار افزایش خواهد یافت. مناسبترین محل این کار در همان مرحله ابتدایی، یعنی در زمان طراحی تراشه است. امروزه طراحی تراشهها با استفاده از نرمافزارهای پیچیده و پیشرفته CAD صورت میگیرد. این ابزارهای CAD توسط شرکتهایی ساخته میشوند که همکاری تنگاتنگی با سازندگان تراشهها دارند. یک نرمافزار CAD بهطور معمول حاوی میلیونها خط کد است که بهسرعت تغییر میکنند. دلیل این تغییرات دائمی هم نیاز به افزودن الگوریتمهای جدید با هدف کمک به طراحان برای افزایش سرعت طراحی و کاهش مصرف مدارهای تراشه است. در نتیجه، گنجاندن چند خط کد در میان هزاران و شاید هم میلیونها خط کد با هدف تغییر در طراحی سختافزار، کار سختی نخواهد بود. نکته نگرانکننده این است که این کار در بیش از یک نقطه از مسیر تولید تراشه قابل اجرا است. مطلب دیگر این است که برخی بلوکهای رایج در مدارها مانند شتابدهندههایی که وظیفه رمزنگاری و آشکارسازی را برعهده دارند، معمولاً توسط تولیدکنندگان ثالث طراحی میشوند.

مرحله حساس دیگری که میتوان در طی آن اقدام به دستکاری تراشه کرد، زمان تولید است. نگرانی از بابت این مرحله در دهههای گذشته و زمانی که تولید تراشه سوددهی بیشتری داشتند و شرکتها میتوانستند تولید این قطعه را در داخل خطوط تولید خود انجام بدهند، کمتر از امروز بود. در سالهای اخیر سرمایه لازم برای راهاندازی خط تولید تراشه بالغ بر ده میلیارد دلار شده و هزینه تحقیقات و توسعه نیز بهطور روزافزون در حال افزایش است. با وجود این هزینههای سنگین، سازندگان تراشه بیشتر روی برونسپاری خدمات به شرکتهای مستقر در چین، کره جنوبی، تایوان و ایالات متحده متکی شدهاند. این راهبرد موجب خواهد شد تا عملیات تکمیل طراحی تخصصیتر صورت گیرد. با وجود اینکه دلیلی برای مشکوک شدن به افزودن آلودگی سختافزاری به تمام تراشههای تولیدی در این روش وجود ندارد، اما نمیتوان احتمال تغییرات ناخواسته در طراحی تراشهها و در نتیجه دستکاری کل تراشههای تولیدی یا بخشی از آنها را نادیده گرفت.

تقسیم بررسی

برش مقطعی از تراشه آزمایشی 130 نانومتری (چپ) لایه ترانزیستور را در پایین و شش لایه فلزی را در بالای آن نشان میدهد. ترانزیستور و نخستین لایه فلزی در «گلوبال فاندریز» سنگاپور تولید شدهاند. دومین لایه از پنج لایه باقیمانده توسط آیبیام و در ایالات متحده تولید شده و تراشه در مؤسسه علوم، فناوری و تحقیقات استنفورد (A*STAR) تکمیل شده است. مدار بررسی که قادر است هر گونه عملیات غیرعادی را شناسایی کند، بین لایه ترانزیستور و سوییچهای RRAM در میان لایههای پنجم و ششم تقسیم شده است. این سوییچها میتوانند پس از اتمام فرآیند تولید تراشه تنظیم شوند. همان طور که در شکل سمت راست مشاهده میشود، مدار بررسی از طریق مقایسه مشخصههای اطلاعات روی خروجی بلوک مدار و اطلاعاتی که مستقیم و توسط مدار بررسی پیشبینی میشود، کار میکند.

مقامهای دولتی مسئول کاملاً از این تهدیدها آگاهاند و در راستای کمک به آگاهیرسانی، برنامهای را با نام «تولید معتبر» با هدف اعتبارسنجی سازندگان حاضر در زنجیره تأمین تعریف کردهاند. سازندگانی که به کار روی این تراشههای «معتبر» مجاز هستند، عموماً به شرکتهایی منحصر خواهند بود که در درون مرزهای ایالات متحده حضور دارند. این کار باعث میشود تا دسترسی به تراشههای پیشرفته محدود شود. بسیاری از این تولیدکنندگان مجاز ایالات متحده قادر نیستند سرمایهگذاری سنگین بکنند و تراشههایی تولید میکنند که به فناوری حداقل ده سال یا بیشتر متعلق هستند. علاوه بر این، تمرکز برنامه مذکور در این کشور بیشتر روی تراشههایی با کاربردهای نظامی است که در ساخت ابزارهایی مانند انواع سلاحها و هواپیماها به کار گرفته میشوند.

مدارهای مجتمع به کار رفته در تولید ابزارهای حیاتی غیرنظامی مانند سیستمهای کامپیوتری ویژه تجهیزات پزشکی یا نیروگاههای هستهای غالباً در آن سوی آبها تولید میشوند و مشمول چنین سطحی از موشکافیهای مرتبط با زنجیره تأمین نخواهند بود.

آنچه همگان خواهان آن هستیم، یافتن روشی آسان، سریع و کمهزینه است و اینکه مشخص کنیم آیا در داخل یک تراشه، تروجان سختافزاری پنهان شده است یا خیر. در این راه چه چیزی را باید جستوجو کرد؟ محققان هنوز در حال بررسی قابلیتهای تروجانهای سختافزاری برای انجام حملات مختلف هستند. آنچه مشخص است این است که تشخیص چنین حملههایی کار بسیار دشواری خواهد بود.

محققان دانشگاه ایلینوی در سال 2008 و در جریان یکی از آزمایشهای انجام شده، موفق به طراحی مدار نفوذی کوچکی شدند که دسترسی به نواحی امنیتی تراشه را میسر میساخت. از این تروجان میتوان برای تغییر کد شناسایی برنامه آلوده استفاده کرد. به این ترتیب، مهاجمان قادر خواهند بود تا هر گونه دسترسی و عملیاتی را روی هر اطلاعاتی که مایل باشند صورت دهند. جای دادن چنین تروجانی تنها به حداکثر هزار ترانزیستور نیاز دارد که در مقایسه با یک میلیون و هشتصد هزار ترانزیستور موجود روی یک تراشه، از لحاظ تعداد تنها 05/0 درصد افزایش را موجب خواهد شد. این میزان اندک حقیقت دشواری را آشکار میکند؛ برای خرابکاری و دستکاری یک تراشه به تغییرات بسیار نیاز نخواهد بود. در واقع، این امکان وجود دارد که حتی جای دادن مدارهای اضافی هم لازم نباشد. مطالعات جدید نشان میدهند که حتی تغییرات اندک روی مشخصههای الکتریکی ترانزیستورهای موجود نیز میتواند امنیت را با مخاطره روبهرو کند.

مدارهای مجتمع امروزی محصولات بینالمللی محسوب میشوند، اما اعتماد چیزی نیست که از ابتدا ساخته شود.

چطور میتوان به دستکاری در تراشهها پی ببریم؟ شاید به این فکر کنید که با قرار دادن تراشه ساخته شده در زیر میکروسکوپ خواهید توانست این موضوع را مشخص کنید. این روش شاید تا اواخر دهه 1970 میلادی پاسخگو باشد. در آن زمان، اینتل ریزپردازنده 4004 خود را معرفی کرده بود. این ریزپردازنده از حدود 2300 ترانزیستور تشکیل شده بود که هر یک با اندازه 10 میکرومتر بهسادگی در زیر میکروسکوپ قابل رؤیت بودند، اما مدارهای مجتمع امروزی بحث جداگانهای دارند. این مدارها بهراحتی میتوانند شامل میلیاردها ترانزیستوری باشند که اندازه هر کدام به میزان یک صدم نمونههای موجود روی تراشه 4004 کوچک شده هستند. با وجود اینکه برای این کار میتوان از میکروسکوپ الکترونی استفاده کرد، اما این فرآیند مخرب محسوب میشود. برای دسترسی به لایه ترانزیستورها باید یک لایه فلزی را که روی آن وجود دارد، برداریم. برای این کار یا باید از مواد شیمیایی برای حل کردن لایه فلزی استفاده شود یا بهصورت فیزیکی اقدام به ساییدن لایه فلزی کنیم.

راهحل مستقیم حل این مشکل تخریب یک نمونه از تراشه و آزمایش روی آن است. چنانچه نمونه مورد آزمایش فاقد تروجان سختافزاری باشد، میتوان این طور فرض کرد که دیگر تراشههای آزمایش نشده در آن سری ساخت خاص فاقد مشکل هستند. هیچ تضمینی برای این فرض وجود ندارد؛ زیرا فرد مهاجم میتواند تنها بخش کوچکی از تراشههای متعلق به یک سری تولیدی را دستکاری کند.

به همین دلیل، پژوهشگران به دنبال یافتن راههای دیگری برای آزمودن تراشهها هستند. یک ایده جدید بر مبنای ارسال اطلاعات مختلف روی مدارهای متعدد و مقایسه نتایج خروجی آنها یا اندازهگیری زمان صرف شده برای عبور اطلاعات از مدارها است. از این روش میتوان در مرحله نهایی کنترل کیفیت و پس از اتمام فرآیند تولید تراشهها استفاده و به این ترتیب تروجانهای احتمالی را آشکار کرد. البته این روش، مناسب نظارت مستمر بر عملیات تراشهها نیست و در نتیجه اگر طراحی تروجان به شکلی باشد که چند ماه یا چند سال پس از خروج از خط تولید فعال شود، این روش کمکی به ما نخواهد کرد.

دانشمندان در مرکز تحقیقاتی توماس جی واتسون شرکت آیبیام در یورکتاون هایت نیویورک در حال تحقیق روی روشهایی هستند که این گونه تروجانهای تأخیری را شناسایی کنند. روش کار به این شکل است که ابتدا تعدادی از تراشههای متعلق به یک سری تولید انتخاب میشوند و سپس با بررسی مشخصههایی مانند مصرف انرژی، درجه حرارت و حتی میزان میدان مغناطیسی ایجاد شده حول تراشه، اقدام به تعریف نوعی «اثر انگشت» برای آنان میکنند. ایده اصلی بر این اساس است که تروجانها احتمالاً بر ویژگیهای خصوصی تراشه تأثیر میگذارند و این تأثیر به گونهای است که حتی به اینکه تروجان فعال باشد نیز نیازی نخواهد بود. در مرحله بعد تحلیلهای آماری به شناسایی تراشههای آلوده کمک خواهند کرد. در مرحله آخر نیز با آزمایش تراشهها در زیر میکروسکوپ الکترونی از نبود تروجان در لابهلای مدارهای آنها اطمینان حاصل خواهد شد. اگر تراشه مورد آزمایش با موفقیت از آزمایش عبور کرد، از آن بهعنوان معیاری برای سنجش دیگر تراشههای موجود در آن سری تولیدی استفاده خواهد شد. تطابق نداشتن «اثر انگشتها» نشاندهنده وجود یک تروجان سختافزاری داخل تراشه خواهد بود.

استفاده از این روش مشکلات خاص خود را دارد. برای مثال، این روش نمیتواند دستکاری جزیی در مدارها مانند اضافه کردن یک «دریچه یای انحصاری» (Exclusive OR) با استفاده از چند ترانزیستور را آشکار کند. دلیل این امر این است که حتی تراشههای سالم و عاری از آلودگی نیز به خاطر تفاوت در نوع ترانزیستورها و اتصالات آنان، انحرافات جزیی را از مشخصههای فیزیکی طبیعی نشان میدهند. میزان این اختلافات و تفاوتهای موجود در مشخصههای الکتریکی و حرارتی از یک تراشه به تراشه دیگر متغیر است. در نتیجه، این اختلافات طبیعی و اجتنابناپذیر میتواند تأثیری همانند یک تروجان کوچک از خود برجای بگذارد.

اکنون باید به این مطلب فکر کرد که چگونه میتوان با استفاده از زیستبوم نیمهرساناها نسبت به افزایش امنیت زنجیره تأمین تراشهها اقدام کرد.

از آنجا که تصویربرداری میتواند وجود تروجانهای کوچکتر را به ما نشان دهد، برخی محققان هنوز امید خود را به این راهحل از دست ندادهاند. در سال 2011، یک گروه تحقیقاتی به سرپرستی مایکل باجورا از مؤسسه علوم اطلاعات دانشگاه کالیفرنیای جنوبی گزارشی را مبنی بر دستیابی به روشی برای عکسبرداری از تراشه بدون آسیب زدن به آن منتشر کردند. در این روش بهجای استفاده از میکروسکوپ الکترونی (که فقط تصویری از سطح تراشه را نمایش میدهد) از اشعه اکس برای تصویربرداری از زوایای مختلف تراشه استفاده میشود. به این ترتیب و با کنار هم گذاشتن نتایج دوبعدی موفق شدند رندری سهبعدی از تراشه ایجاد کنند. با استفاده از این میکروسکوپ اشعه اکس میتوان جزییاتی با دقت 30 نانومتر را مشخص کرد و در نتیجه هر گونه دستکاری را حتی روی پیشرفتهترین تراشههای موجود شناسایی کرد. با وجود این، متأسفانه هنوز تراشهها در برابر تشعشعات آسیبپذیر هستند و کماکان کار و زمان زیادی نیاز است تا مطالعات بیشتری روی این روش صورت پذیرد.

چنین چالشهایی موجب شدهاند تا ایجاد برخی تغییرات در فرآیند ساخت تراشهها بهعنوان یک شیوه مؤثر دیگر مورد توجه قرار گیرد. ایده این قضیه که به آن «تولید مجزا» گفته میشود، این است که در ابتدا فرآیند ساخت تراشه را به دو مرحله تقسیم میکنند. مرحله نخست به حساسترین (و البته هنرمندانهترین) مرحله، یعنی لایه ترانزیستورها اختصاص دارد و در ادامه صفحههای فلزی حاوی سیمکشیهای پرجزییات برای برقراری ارتباط بین ترانزیستورها روی لایه نخست قرار خواهد گرفت. در مرحله دوم، تراشهها برای تکمیل شدن برای یک سازنده باسابقه و مورد اعتماد ارسال خواهد شد. این سازنده پس از تکمیل ارتباطات روی تراشه، لایه فلزی سیمبندی شده آخر را نصب و تراشه را برای پخش روانه بازار میکند.

نکته کلیدی در این ایده از این قرار است که چنانچه چند لایه نخست تراشه توسط تولیدکننده غیرمطمئن ایجاد شده باشد، تشخیص نحوه کارکرد تراشه از میان دریایی از ترانزیستورها و ارتباطات بین آنان برای کارگران مونتاژکننده غیرممکن خواهد بود. در عوض، این ناآگاهی باعث میشود تا یک هکر مشتاق قادر نباشد تروجانی را به شکلی کشفناپذیر در داخل تراشه جاگذاری کند.

به طور کلی، استفاده از روش «تولید مجزا» به نفع همه خواهد بود. با این روش تولیدکنندگان قدیمی و معتبر که عموماً از سطح فناوری پایینتری استفاده میکنند، قادر خواهند بود از ظرفیتهای تولیدی شرکتهای نامطمئن بهرهمند شوند، بدون اینکه ناچار شوند همه اطلاعات را درباره تولید تراشه فاش کنند. IARPA با در نظر گرفتن این موضوع برنامه جدیدی را با نام «تراشههای مجتمع معتبر» (Trusted Integrated Chips) در سال 2011 آغاز کرد. هدف این برنامه یافتن روشهایی برای پیادهسازی هرچه بهتر ایده «تولید مجزا» بود.

برنامه IARPA بهویژه با هدف شناسایی تروجانهای اضافه شده به تراشههای تولیدی تعریف شده است. روشی که ما روی آن کار کردیم، در واقع توسعه «تولید مجزا» بوده و به گمان ما میتواند راهحل کاملی برای این مشکل باشد. مشکلی که نه تنها آشکارکننده تروجانهای جاسازی شده در زمان تولید خواهد بود، بلکه حتی تروجانهایی را هم که در زمان طراحی در میان تراشه جای داده میشوند، شناسایی خواهد کرد. مشکلی که حتی روش «تولید مجزا» هم قادر به حل آن نیست. چنین امنیتی هزینه خود را خواهد داشت و صد البته این هزینه متناسب با تعداد ترانزیستورها خواهد بود. در مراحل اولیه، هدف ما ایجاد مدارهای جدید برای هر تراشه، آن هم به گونهای بود تا بتوان حتی پس از خریداری و نصب تراشه را تحت نظر قرار داد. این مدارهای جدید وظیفه آشکارسازی خطاها را برعهده خواهند داشت. سالها است از این روش برای خطایابی مستمر انواع محاسبات ماشینی و یافتن خطاهای سختافزاری و افزایش قابلیت اطمینان در کامپیوترهای رده بالا استفاده میشود.

خطایابی همزمان روی بخشها یا بلوکهای مدارهای داخلی یک تراشه صورت میگیرد. نکته طلایی در طراحی یک فرآیند خطایابی، یافتن روشی اقتصادی برای اطمینان از عملکرد صحیح یک بلوک است. بهطور معمول، این دستاورد از طریق طراحی مدارها آن هم به گونهای که به موازات یک بلوک کار کنند، امکانپذیر خواهد بود. این مدارها با ایجاد یک میانبر محاسباتی اقدام به پردازش اطلاعات ورودی بلوک میکنند. چنانچه طراحی بهخوبی صورت گیرد، نتایج حاصل با زمانی که بلوک در وضعیت طبیعی کار کند، یکسان خواهند بود.

برای مثال، یکی از معمولترین بررسیها «عملکرد توازنی» است که به شما نشان خواهد داد تعداد «1»های منطقی ایجاد شده یک محاسبه در یک بازه مشخص فرد یا زوج هستند. چنانچه نتیجه مقایسه در انتهای «مدار بررسی» با نتیجه خروجی «مدار بلوک» یکسان باشد، به احتمال زیاد مدار بلوک عاری از خطا است. در غیر این صورت و چنانچه مغایرتی مشاهده شود، معنای آن این است که یک جای کار ایراد دارد. این طرح برای تشخیص خطاهای تصادفی ایدهآل است، اما همین روش در تله یک تروجان که با دقت و زیرکانه طراحی شده باشد، گرفتار خواهد شد. برای مثال، یک مهاجم باهوش که از بهکارگیری «بررسی توازن» مطلع است، میتواند مداری را در تراشه تعبیه کند که با دستکاری چند بیت موجب شود تا با تغییر ندادن در تعداد «1»های تولید شده، حضور تروجان مخفی باقی بماند.

برای جلوگیری از این ترفند، دو راه را برای پنهان ساختن عملکرد مدارهای بررسی ابداع کردیم. روش نخست بر پایه تغییر در طراحی بررسیکننده تعریف شده است. در ابتدا، یک ناپایداری (که آن را توازن تصادفی مینامیم) در عملکرد توازنی ایجاد کردیم. یک عملکرد توازنی عادی میتواند 10 بیت را بگیرد و با استفاده از آن تعداد «1»ها را بشمارد. در روشی که ما از آن استفاده کردیم، هر مدار بررسی طوری تنظیم شده بود تا نمونههای تصادفی 10 بیتی را در نظر بگیرد و برای مثال بیتهای دوم، پنجم، هفتم و هشتم را انتخاب کند. طراحی تراشه به صورتی انجام شده تا تنظیمات مربوط به نمونهگیری بررسیکننده کاملاً تصادفی صورت پذیرد. همچنین، تنظیمات مدار بررسی نیز میتواند بهطور سختگیرانه طراحی شود تا از بقیه تراشه مستقل باشد و به این ترتیب امکان هر گونه سازش و تبانی را در مرحله طراحی از بین ببرد.

مرحله دوم پنهان کردن عملکرد مدار بررسی در زمان تولید و به وسیله ایجاد برخی اتصالات با سوییچهای قابل برنامهریزی به گونهای که تنها پس از اتمام ساخت تراشه تنظیمات آنان انجام شود، خواهد بود. با این روش، نحوه طراحی مدار بررسی برای مونتاژکنندگان تشخیصناپذیر شده و هرگونه دستکاری در تراشه بسیار مشکل خواهد شد.

چند تنظیم کوچک میتواند از تراشهها در برابر مدارهای آلوده محافظت کند.

برای ساخت این سوییچها از حافظههایی با نام «حافظههای مقاومتی» (Resistive RAM) یا RRAM استفاده شده است. یک سلول RRAM از یک لایه عایق تشکیل شده است که بین دو لایه فلزی قرار دارد. با انتخاب عایق مناسب، RRAM میتواند با دریافت یک ولتاژ بسیار اندک بین دو وضعیت مقاومت پایین و بالا سوییچ و حالت خود را حتی در صورت نبود هرگونه منبع انرژی حفظ کند. به این ترتیب، میتوان از این حافظه بهعنوان سیمکشی قابل برنامهریزی استفاده کرد و برحسب نیاز با وارد کردن یک ولتاژ مدار را بسته یا باز کنیم.

سوییچهای قابل برنامهریزی چیز جدیدی نیستند. بسیاری از تراشههایی که در دستگاههای صوتی و تصویری، خودروها یا تجهیزات پزشکی وجود دارند، با استفاده از مدارهای FPGA (سرنام Arrays Field Programmable Gate) طراحی شدهاند. این مدارها در واقع مدارهای استانداردی هستند که پس از ترک خط تولید، عملکردهای قابل برنامهریزی خود را در سلولهای حافظه بر مبنای ترانزیستور به کار میگیرند. اما RRAM برای این کاربرد قدری جذابتر به نظر میآید؛ زیرا حجم آن فشردهتر است و مکان کوچکتری را اشغال میکند. آزمایشها نشان دادند اگر حافظههای FPGA بهجای استفاده از فرم همیشگی شش ترانزیستوری، با استفاده از سلولهای حاوی یک ترانزیستور و دو RRAM ساخته شود، مساحت تراشه تا 40 درصد و مصرف انرژی آن تا 28 درصد میتواند کاهش داده شود. اضافه بر آن، RRAM را برخلاف حافظههای سنتی ترانزیستوری میتوان در کنار اتصالات فلزی و در بالای لایه فعال ترانزیستورها در داخل تراشه قرار داد. ضمن اینکه اگر نخواهید از روش تولید مجزا استفاده کنید، میتوان آنها را در هر مرحله از تولید لایههای فلزی که مایل هستید جای دهید. پروژه ما در سال 2012 شروع شد. در همان مرحله نخست طراحی تراشه را با بهکارگیری فناوری 13/0 میکرونی آغاز کردیم. ترانزیستورها و مدارهای بررسی مبتنی بر ترانزیستور همراه لایه فلزی در کارخانه گلوبال فاندریز کشور سنگاپور تولید شدند. دیگر لایههای فلزی در یکی از سایتهای تولیدی شرکت آیبیام و در بورلینگتون به تراشه اضافه شدند. پس از آن RRAM و سپس آخرین لایه فلزی تولید شد.

در جریان این فرآیند مقدار زیادی شتابدهنده برای متراکمسازی داده و FPGA ایجاد شدند. تونی وو و دیگر اعضای آزمایشگاه ما تراشهها را روی برد مدار نصب کردند و با اتصال آن به یک کامپیوتر آزمایشهای زیادی را با استفاده از شبیهسازی انواع حملات صورت دادند. نتیجه آزمایشها نشان دادند مدارهای بررسی که در داخل شتابدهنده ایجاد شده، علاوه بر اینکه تأثیری بر سرعت تراشه ندارد، فقط یک درصد از مساحت تراشه را اشغال میکند. اعضای گروه از طریق تغییر در خروجی گروههای متفاوتی از بلوکهای مداری، حملات تروجانی متنوعی را روی تراشه انجام دادند. مدار بررسی تراشه موفق به تشخیص 9998/99 درصد از مجموع ده میلیون حمله سختافزاری شد که روی تراشه صورت گرفت.

این آزمون توانست تروجانهایی را تشخیص دهد که مستقیم روی مدار عملیاتی تراشه تعبیه شده بودند. حتی حملات replay نیز تشخیص داده شدند. این حملات با ضبط خروجیهای معتبر بلوک مدار و سپس «بازپخش» آن در هنگام حمله چنان وانمود میکند که همه چیز عادی است و مشکلی وجود ندارد، اما مدار بررسی با محدودیتهایی مواجه است. این مدار قادر است تا اطلاعاتی را که از طریق کانالهای عادی ورودی ـ خروجی تراشه منتشر میشوند، دریافت کند. اما نمیتواند تروجانی که بهصورت انفعالی اطلاعات را استخراج میکند و بعد آنها را بهصورت بیسیم و به وسیله مدارهای بیسیم ارسال میکند، شناسایی کند. در حال حاضر، مطالعاتی در زمینه مقابله با چنین حملاتی در دست انجام است.

چنانچه حتی از تولید مجزا نیز استفاده نشود، تلاشهای صورت گرفته برای طراحی مدار بررسی و RRAM قابل برنامهریزی، کار جاگذاری تروجان سختافزاری را برای یک مهاجم بسیار سخت خواهد کرد. نظر ما این است که با وجود استفاده از هرگونه راهبرد برای محافظت در برابر دستکاری، حتی در مواردی که از تولید مجزا، آزمون و روش عکسبرداری مخرب استفاده شود، هنوز بسیار دشوار است که بتوان با اطمینان و پیش از روانه شدن تراشه به بازار نسبت به آلوده بودن آن به تروجان سختافزاری نظر قطعی داد؛ زیرا مدارهای کوچک بهسادگی در میان انبوهی از ترانزیستورها و سیمکشیهای آنان پنهان خواهند شد.

با وجود اینکه مدار بررسی ما به گونهای طراحی شده تا بتواند تراشهها را بهصورت مستمر تحت نظارت داشته باشد، اما نمیتوان بهطور کامل از این عمل جلوگیری کرد. به این ترتیب، چالش اصلی بر سر یافتن پاسخی برای این پرسش است: «اگر یکی از این مدارها حمله یک تروجان را تشخیص دهد، چه باید بکنیم؟» آیا یک خاموش و روشن کردن ساده میتواند حمله بعدی را چند ماه یا حتی چند سال به تعویق بیاندازد؟ آیا راهی وجود دارد مدارهایی را برای بازیابی تراشه در داخل آن تعبیه کنیم و با استفاده از فناوریهایی تصحیح خطا مانند ایجاد نقاط بازگشت برای ذخیره اطلاعات در بازههای بحرانی، پس از حمله نسبت به تصحیح همه چیز اقدام کنیم؟ آیا باید با ایجاد نقاط بازگشت بیشتر در سیستمهای کنترلی حساس، برای مقابله با تهدیدات و آسیبهای احتمالی تروجانها در داخل دستگاهها و تجهیزات خود تراشههای بیشتری را تعبیه کنیم؟

اینها پرسشهایی هستند که با پیشرفت فناوریهای محافظتی مربوط به تروجانها بیش از پیش نیاز به پاسخ به آنان احساس میشود. اینک در مرحله دوم پروژهای قرار داریم که هدف آن بهکارگیری فناوری پیشرفتهتر 28 نانومتری برای فرآیند تولید تراشههای پیشرفته و یک پله صعود نسبت به نقطهای است که امروز در آن ایستادهایم.

اکنون باید به این مطلب فکر کرد که چگونه میتوان با استفاده از زیستبوم نیمهرساناها نسبت به افزایش امنیت زنجیره تأمین تراشهها اقدام کرد. تولید مجزا میتواند کمک خوبی باشد، اما استفاده از این روش هزینه تولید تراشه را بهطور ملموس افزایش میدهد و فرآیند لجستیک را با پیچیدگی مواجه میسازد. شاید به مشوقهای بیشتری برای ترغیب شرکتهای سازنده تراشه و سرمایهگذاران آنان به همکاری بیشتر نیاز باشد.

مقابله با تهدید تروجانهای سختافزاری به تصمیمات دشوار و انبوهی از تغییرات در روش تولید نیازمند خواهد بود. این حرف به این معنا است که باید مفهوم اعتماد را برای خود بازتعریف کنیم. در هر صورت، با تلاش مناسب میتوان شرایطی به وجود آورد تا تعداد حملات کاهش پیدا کند و تأثیرات آن نیز کمرنگتر شود. شاید با این روش بتوان داستان اسب تروا را به اعماق افسانههای تاریخی، یعنی همان جایی که به آن تعلق دارد، بازگردانیم.

ماهنامه شبکه را از کجا تهیه کنیم؟

ماهنامه شبکه را میتوانید از کتابخانههای عمومی سراسر کشور و نیز از دکههای روزنامهفروشی تهیه نمائید.

ثبت اشتراک نسخه کاغذی ماهنامه شبکه

ثبت اشتراک نسخه آنلاین

کتاب الکترونیک +Network راهنمای شبکهها

- برای دانلود تنها کتاب کامل ترجمه فارسی +Network اینجا کلیک کنید.

کتاب الکترونیک دوره مقدماتی آموزش پایتون

- اگر قصد یادگیری برنامهنویسی را دارید ولی هیچ پیشزمینهای ندارید اینجا کلیک کنید.

نظر شما چیست؟